8

В.Ф. Жирков, А.П. Калинин

ности. В данном устройстве для всего процесса обработки генерирует-

ся 17 импульсов: один для загрузки и 16 для преобразования.

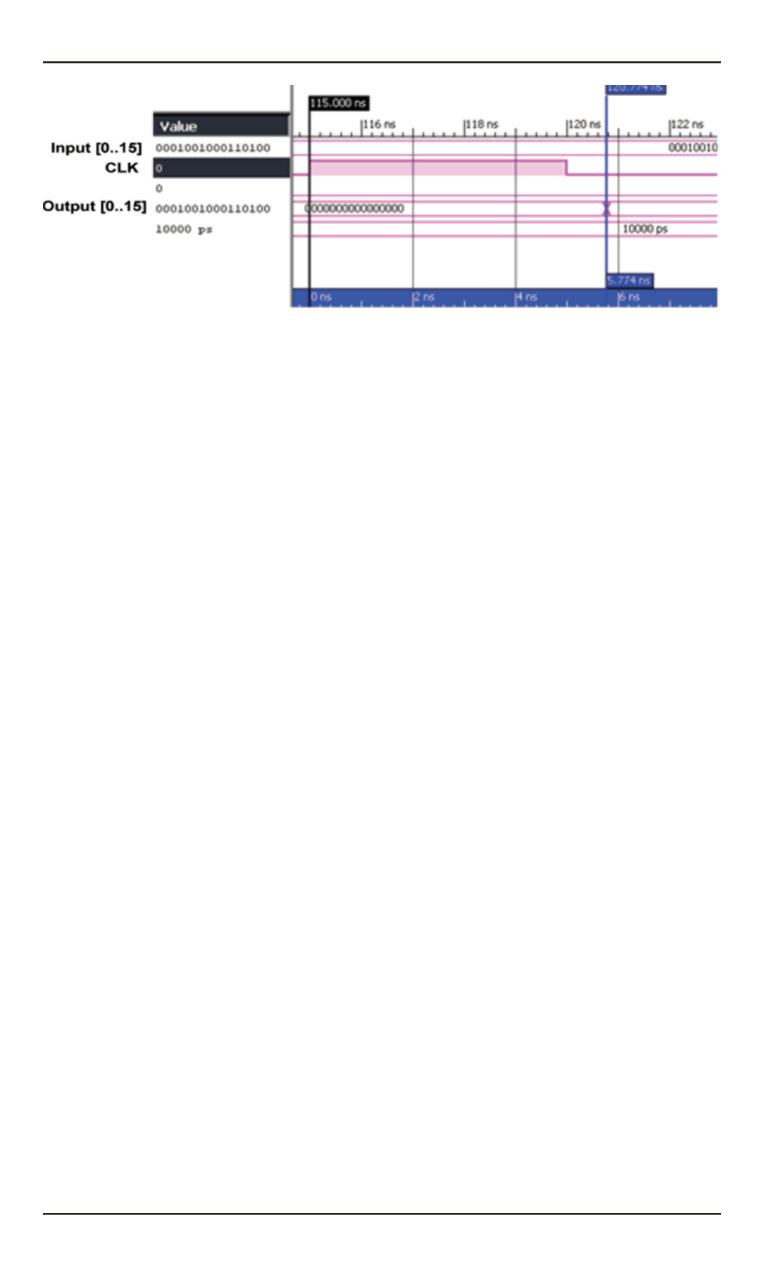

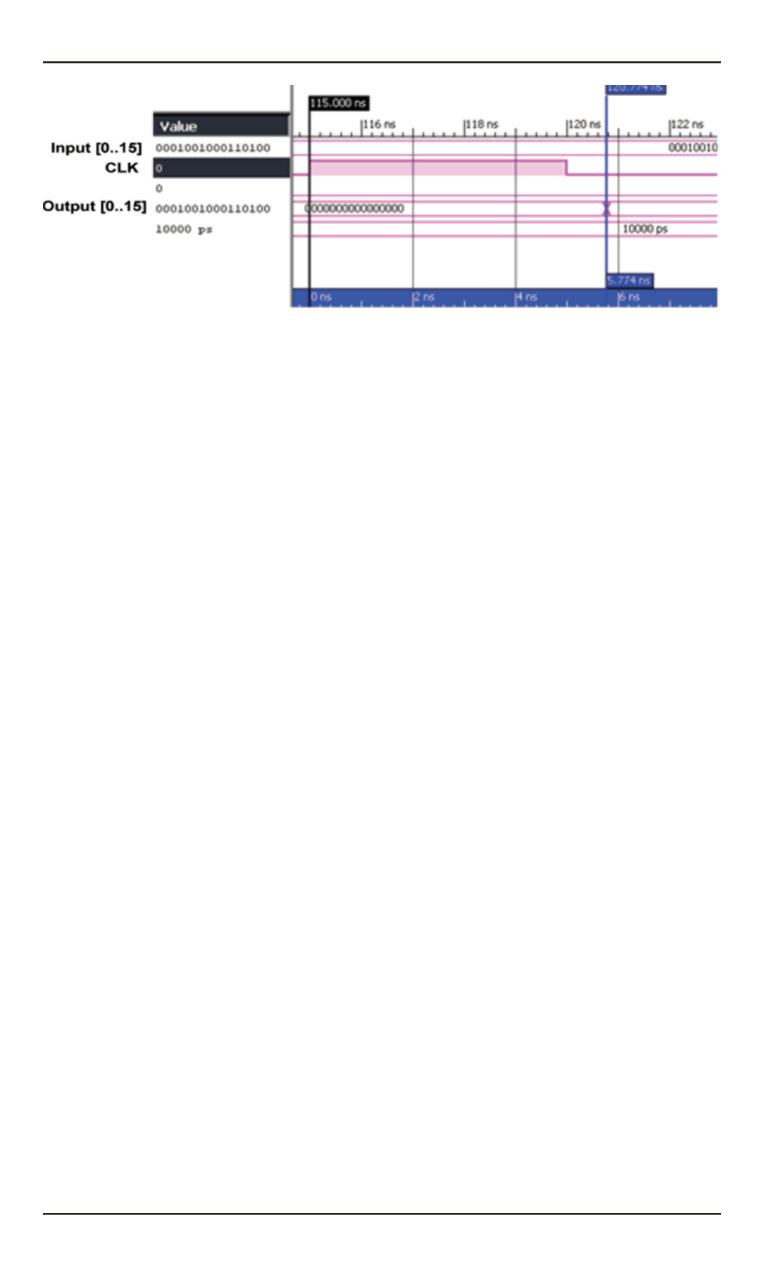

Для тестирования преобразователя и оценки его временных па-

раметров было проведено моделирование с помощью стандартного

средства Test Bench САПР Xilinx ISE 14.7. Данное средство позволяет

моделировать работу любых устройств, описанных на языках VHDL

или Verilog, строить временные диаграммы тестируемых устройств.

Для моделирования создан специальный файл поведенческого моде-

лирования, в котором описываются все временные изменения входных

сигналов.

При моделировании получены данные, по которым установлено,

что время задержки распространения сигнала в регистре сдвига не

превышает 4 нс. Время задержки распространения в тракте преобра-

зователя, состоящего из мультиплексора, десятичного регистра и ЭП,

не превышает 10 нс. При тактовой частоте 100 МГц собственно время

преобразования 4-разрядного ДДК целого числа составляет ~200 нс,

а с учетом несинхронизированного прихода команды преобразования

с тактовыми импульсами не превышает 250 нс. Время преобразования

8-разрядного ДДК дроби составляет 400 нс.

ЛИТЕРАТУРА

[1] Гришин Ю.Р., Казаринов Ю.М., Катиков В.М. и др.

Проектирование им-

пульсных и цифровых устройств радиотехнических систем

. Москва, Высш.

шк., 1985, 319 с.

[2] Титце У., Шенк К.

Полупроводниковая схемотехника

. Москва, Мир, 1982,

512 с.

[3] Пухальский Г.И., Новосельцева Т.Я.

Проектирование дискретных устройств

на интегральных микросхемах

. Москва, Радио и связь, 1990, 304 с.

[4] Алексенко А.Г.

Основы микросхемотехники. Элементы морфологии микро-

электронной аппаратуры

. 2-е изд., перераб. и доп. Москва, Сов. радио, 1977,

408 с.

Рис. 4.

Временная диаграмма работы регистра с параллельным вводом и вы-

водом информации