В.Ф. Жирков, И.Д. Маслов

10

В качестве примера на рис. 2 и 3 затенением показано объедине-

ние четырех ЭП-4.

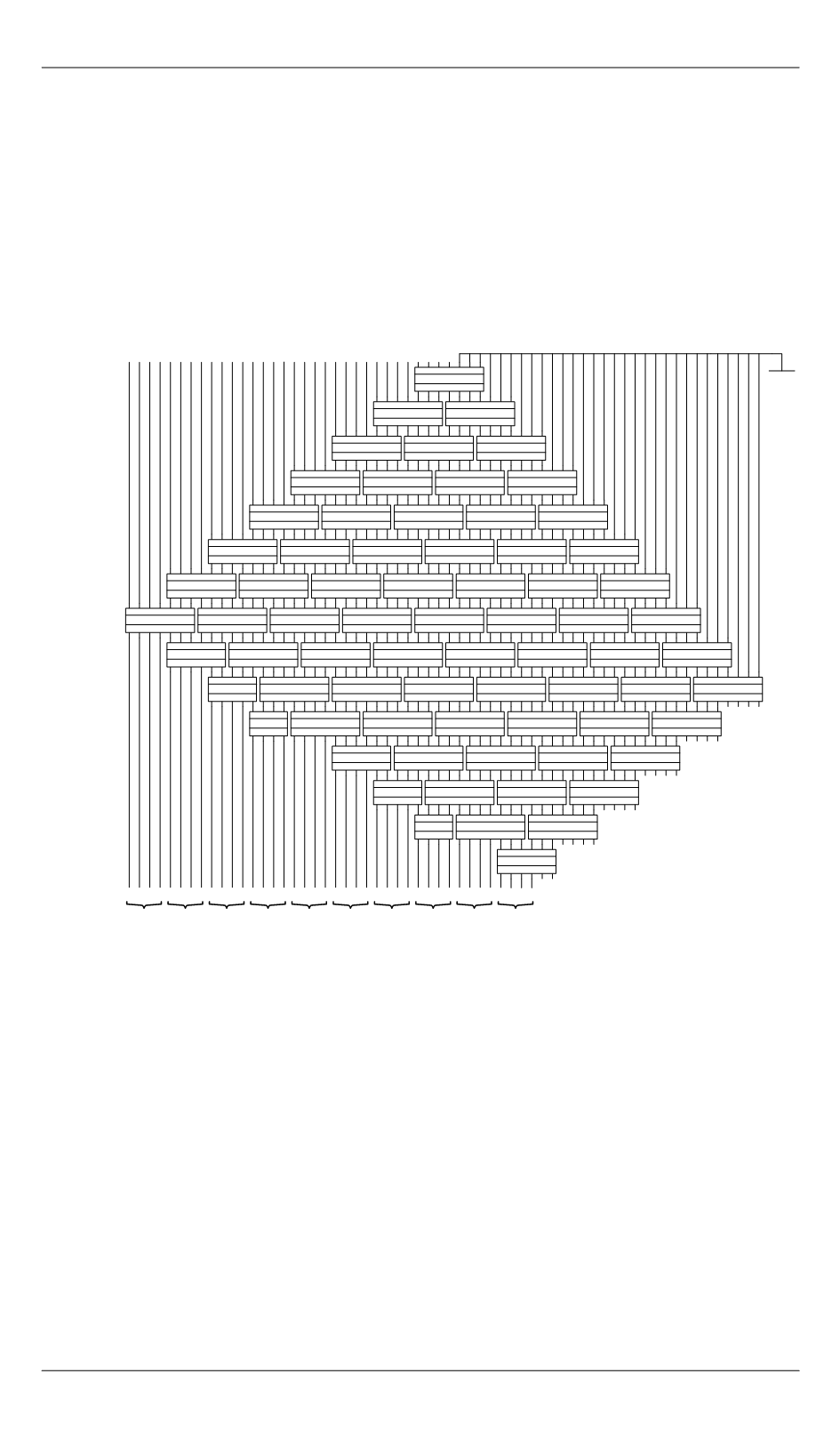

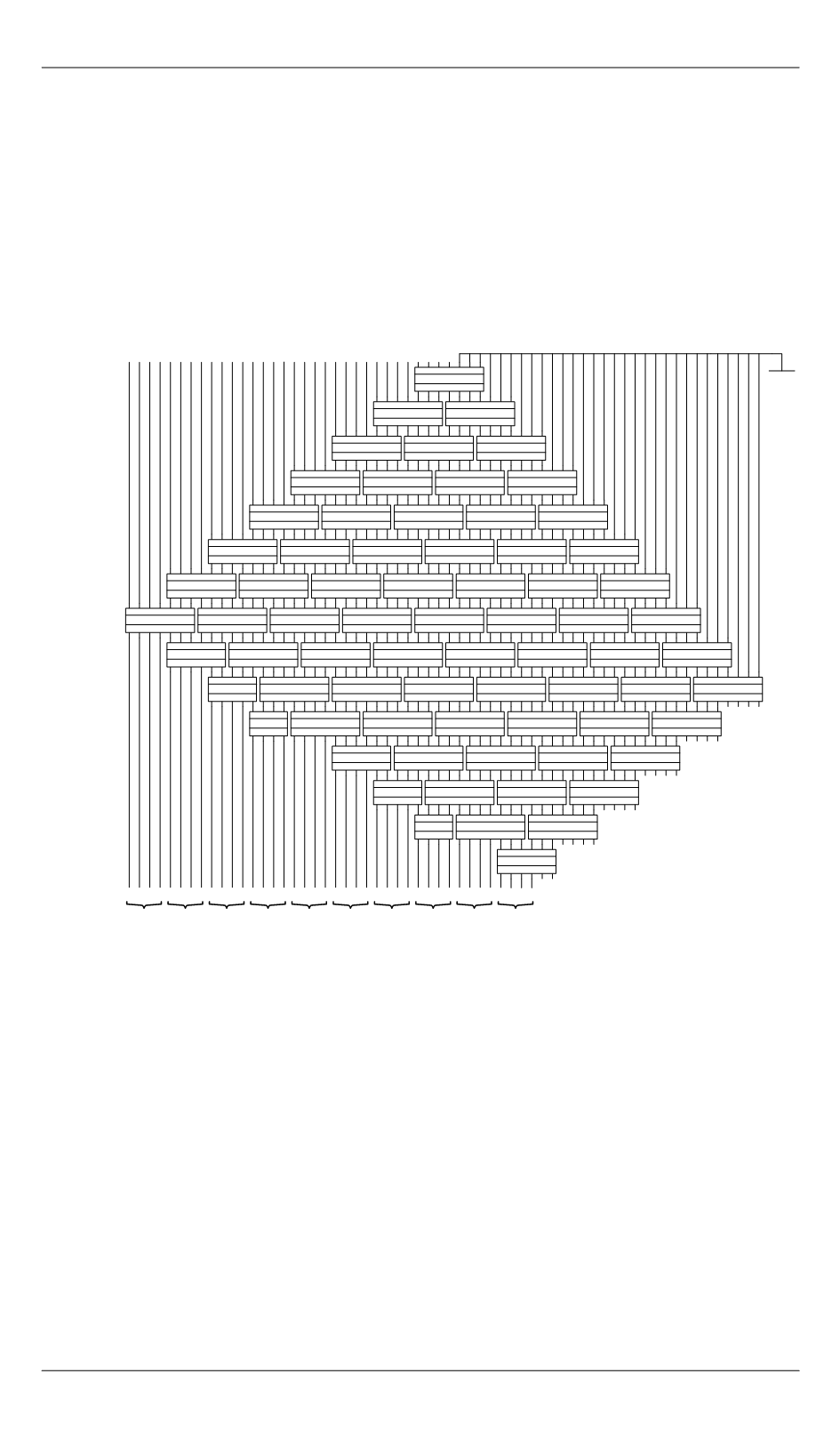

В преобразователе 32-разрядного ДК дроби в ДДК (рис. 5), кроме

ЭП-7, в случае когда число ЭП-4, расположенных по диагонали, не

кратно 4, используются также ЭП-4, ЭП-5 и ЭП-6 (см. рис. 3). Преоб-

разователь ЭП-6 объединяет три ЭП-4 и имеет шесть входов и шесть

выходов. Функционирование ЭП-6 определяется первыми восемью

строками функции (10).

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

в

-1

в

-2

в

-3

в

-4

в

-5

в

-6

в

-7

в

-8

в

-9

в

-10

в

-11

в

-12

в

-13

в

-14

в

-15

в

-16

Х

10

-1

y

0

y

1

y

2

y

3

Х

10

-2

y

4

y

5

y

6

y

7

Х

10

-3

y

8

y

9

y

10

y

11

Х

10

-4

y

12

y

13

y

14

y

15

Х

10

-5

y

16

y

17

y

18

y

19

Х

10

-6

y

20

y

21

y

22

y

23

Х

10

-7

y

24

y

25

y

26

y

27

Х

10

-8

y

28

y

29

y

30

y

31

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20

16 32

X/Y

5 4 2 1

8 4 2 1

10

16

X/Y

5 4 2 1

8 4 2 1

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20

16 32

X/Y

5 4 2 1

8 4 2 1

10

16

X/Y

5 4 2 1

8 4 2 1

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20 40

16 32 64

X/Y

5 4 2 1

8 4 2 1

10 20

16 32

Х

10

-9

y

32

y

33

y

34

y

35

Х

10

-10

y

36

y

37

y

38

y

39

в

-17

в

-18

в

-19

в

-20

в

-21

в

-22

в

-23

в

-24

в

-25

в

-26

в

-27

в

-28

в

-29

в

-30

в

-31

в

-32

Двоично-десятичная

дробь

Двоичнаядробь

Вес тетрад

Рис. 5.

Схема преобразователя 32-разрядного ДК правильной дроби в ДДК

В результате моделирования определено время задержек распро-

странения сигналов LUT

t

зд.р.lut

= 0,4 нс и линий связи

t

л.с

= 1,4…1,6 нс.

Так как LUT реализован в виде оперативной памяти, то

t

зд.р.lut

не зависит

от реализуемой функции. Преобразователь 32-разрядной дроби содер-

жит 15 каскадов, время задержки распространения сигналов в преобра-

зователе составило ~36 нс при реализации на ПЛИС SPARTAN-6 и

ЭП-7 и ~48 нс при реализации на ПЛИС SPARTAN-3 и ЭП-4. Отноше-

ние задержек в логических схемах и линиях связи равно 1: 3 при реали-

зации преобразователя на ЭП-7 и 1:1 при реализации на ЭП-4. Таким

образом, применение ЭП-7 для построения преобразователя уменьшает

число каскадов и, следовательно, время задержки распространения сиг-

налов в линиях связи и в целом в преобразователе.