7

Преобразователь двоично-десятичного кода целых чисел в двоичный код...

преобразования

С

такое устройство должно обеспечить занесение ДДК

целого числа в десятичный регистр из шины входных данных. Затем

УУ вырабатывает серию импульсов для выполнения преобразования,

количество которых определяется разрядностью дроби и требованиями

точности. В данном устройстве для всего процесса приема и преобра-

зования генерируется 17 импульсов: один – для загрузки ДДК преобра-

зуемого целого числа в десятичный регистр и 16 – для преобразования.

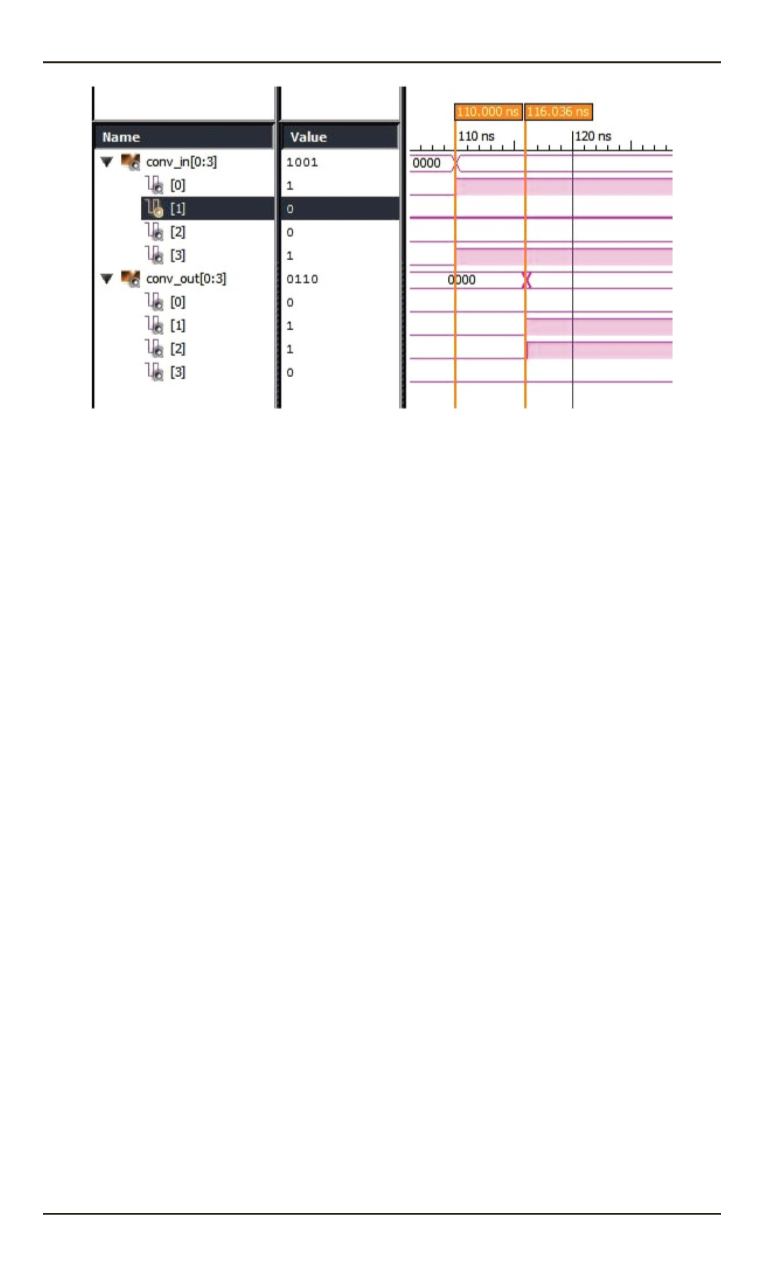

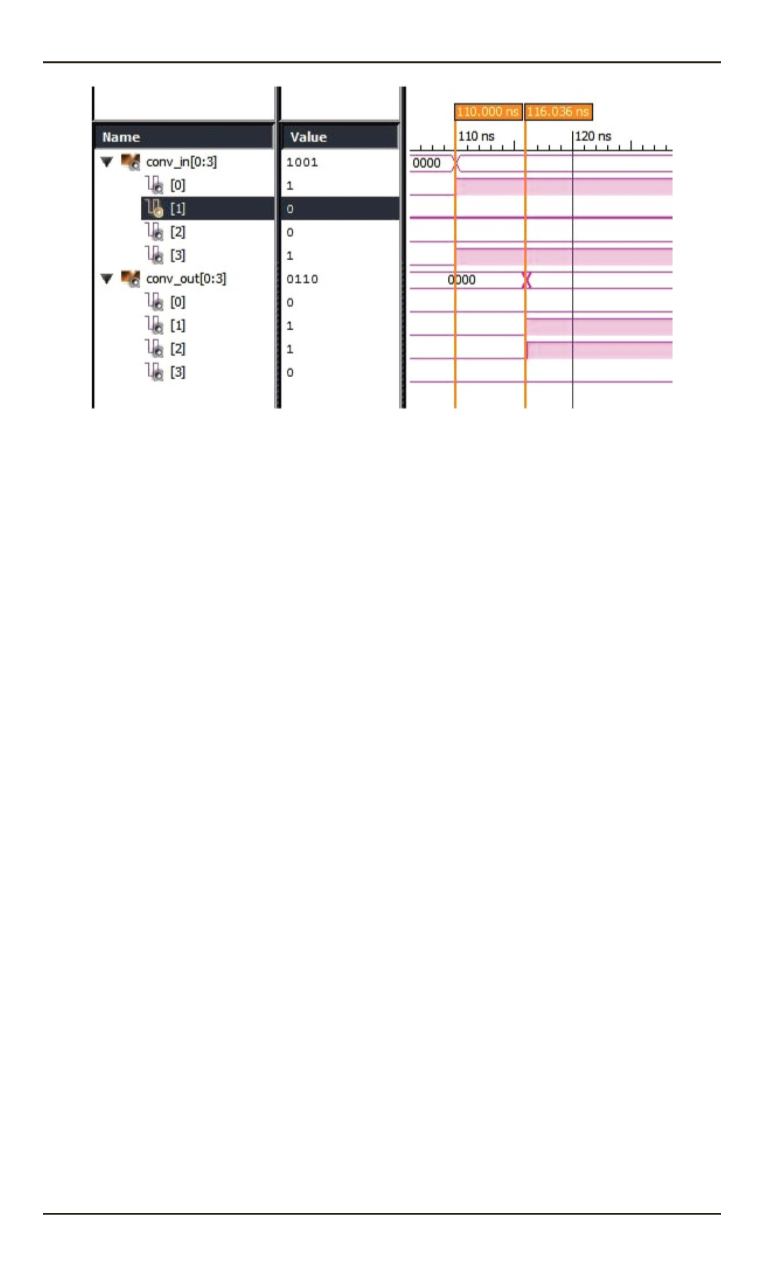

С помощью стандартного средства Test Bench САПР Xilinx ISE 14.7

проведено моделирование для тестирования преобразователя и оценки

его временных параметров. Данное средство позволяет моделировать

работу любых устройств, описанных на языках VHDL или Verilog, для

построения временных диаграмм тестируемых устройств. Создан спе-

циальный файл поведенческого моделирования, в котором описывают-

ся все временные изменения входных сигналов.

По данным, полученным в результате моделирования, установлено,

что задержка распространения сигнала в регистре сдвига не превышает

4 нс. Время задержки распространения в тракте преобразователя, со-

стоящего из мультиплексора, регистра и ЭП, не превышает 9 нс. При

тактовой частоте 100 МГц время преобразования 4-разрядного ДДК

целого числа составляет ~200 нс, 8-разрядного – 400 нс.

ЛИТЕРАТУРА

[1] Гришин Ю.Р., Казаринов Ю.М., Катиков В.М. и др.

Проектирование им-

пульсных и цифровых устройств радиотехнических систем

. Москва, Высш.

шк., 1985, 319 с.

[2] Титце У., Шенк К.

Полупроводниковая схемотехника

. Москва, Мир, 1982,

512 с.

Рис. 3.

Временная диаграмма работы ЭП